# HIGHLY FLEXIBLE MULTI-CHANNEL TIMING DEVICES

- Up to 8 independent channels

- Timings channels configurable as DPLLs or DCOs

- Generates any frequency from 0.5Hz to 1GHz

### **ULTRA-LOW JITTER**

- 150fs RMS (typ) 12kHz to 20MHz

- Suitable for 28Gbps and lower rate interfaces

## PRECISION TIME SYNC.

- Supports cTE < 5ns for G.8273.2 Classes A, B, C, D

- Input to output phase skew< 100ps

- Output to output phase skew < 50ps</li>

#### **APPLICATIONS**

- IEEE 1588

- Synchronous Ethernet

- eCPRI and CPRI

- 28Gbps and lower rates

- 5G fronthaul and backhaul

- Routers / Switches

- OTN and PTN equipment

- Baseband and Radio Units

### **STANDARDS COMPLIANCE**

- ITU-T G.8262

- ITU-T G.8262.1

- ITU-T G.8273.2

# ClockMatrix Family Overview

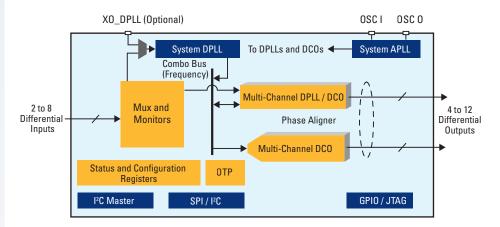

The ClockMatrix<sup>TM</sup> family of multi-channel timing devices reduces the complexity and cost of clock trees by replacing multiple timing chips with a single timing resource. The devices support a wide range of frequencies and signal types at their inputs and outputs.

ClockMatrix devices include two types of timing channels: Digital PLL / Digitally Controlled Oscillator (DPLL/DCO) channels and DCO only channels. Any DCO can free run based on the local oscillator. They can be controlled by external software or they can be connected to a DPLL channel to supply additional outputs and frequencies for that DPLL.

A wide range of simple to complex timing and synchronization applications are covered by the ClockMatrix family using its flexible architecture, a common register set and a few package types.

# ClockMatrix Product Families Telecom System Synchronizers Telecom Port Synchronizers General Purpose Universal Frequency Translators Range of Applications

In the ClockMatrix family, the Universal Frequency Translator (UFT™) devices perform jitter attenuation and frequency translation functions for general purpose applications.

Telecom port synchronizers generate ITU-T compliant clocks for telecom line cards locked to a system synchronizer while the system synchronizers generate ITU-T compliant clocks for telecom systems.

INTEGRATED DEVICE TECHNOLOGY CLOCKMATRIX FAMILY OVERVIEW | 1

# ClockMatrix Family Overview

# **ClockMatrix Family Comparisons**

|                                     | Universal Frequency Translators | Port Synchronizers | System Synchronizers |

|-------------------------------------|---------------------------------|--------------------|----------------------|

| Jitter Attenuation                  | Yes                             | Yes                | Yes                  |

| Frequency Translation               | Yes                             | Yes                | Yes                  |

| Hitless Reference Switching         | Yes                             | Yes                | Yes                  |

| DPLL Loop Filters                   | 17Hz to 12kHz                   | 17Hz to 12kHz      | 0.09mHz to 12kHz     |

| Reference Frequencies               | 1kHz to 1GHz                    | 1kHz to 1GHz       | 0.5Hz to 1GHz        |

| Output Frequencies                  | 0.5Hz to 1GHz                   | 0.5Hz to 1GHz      | 0.5Hz to 1GHz        |

| Align Clocks with Input Sync Pulse  | Yes                             | Yes                | Yes                  |

| Sync Pulse over PWM                 | No                              | Yes                | Yes                  |

| Data over PWM                       | No                              | Yes                | Yes                  |

| EEC1 and EEC2 per G.8262            | No                              | No                 | Yes                  |

| eEEC per G.8262.1                   | No                              | No                 | Yes                  |

| Telecom Boundary Clock per G.8273.2 | No                              | No                 | Yes                  |

# **Universal Frequency Translator Family**

|                     | 8A34041              | 8A34042           | 8A34043         | 8A34044           | 8A34045           |

|---------------------|----------------------|-------------------|-----------------|-------------------|-------------------|

| Inputs (Diff / SE)  | 8 / 16               | 7 / 14            | 2/4             | 4/8               | 2/4               |

| Outputs (Diff / SE) | 12 / 24              | 8 / 16            | 4/8             | 12 / 24           | 12 / 24           |

| DPLL / DCO Channels | 8                    | 4                 | 4               | 4                 | 2                 |

| DCO Channels        | 0                    | 0                 | 0               | 4                 | 6                 |

| Package             | 10 x 10 mm 144-CABGA | 10 x 10 mm 72-QFN | 7 x 7 mm 48-QFN | 10 x 10 mm 72-QFN | 10 x 10 mm 72-QFN |

## **Port Synchronizer Family**

|                     | 8A34011                 | 8A34012              | 8A34013            |

|---------------------|-------------------------|----------------------|--------------------|

| Inputs (Diff / SE)  | 8 / 16                  | 7 /14                | 2/4                |

| Outputs (Diff / SE) | 12 / 24                 | 8 / 16               | 4/8                |

| DPLL / DCO Channels | 8                       | 4                    | 4                  |

| DCO Channels        | 0                       | 0                    | 0                  |

| Package             | 10 x 10 mm<br>144-CABGA | 10 x 10 mm<br>72-QFN | 7 x 7 mm<br>48-QFN |

# **System Synchronizer Family**

|                        | 8A34001                 | 8A34002              | 8A34003            | 8A34004            |

|------------------------|-------------------------|----------------------|--------------------|--------------------|

| Inputs<br>(Diff / SE)  | 8 /16                   | 7 /14                | 2/4                | 2/4                |

| Outputs<br>(Diff / SE) | 12 / 24                 | 8 / 16               | 4/8                | 4/8                |

| DPLL / DCO<br>Channels | 8                       | 4                    | 4                  | 2                  |

| DCO Channels           | 0                       | 0                    | 0                  | 0                  |

| Package                | 10 x 10 mm<br>144-CABGA | 10 x 10 mm<br>72-QFN | 7 x 7 mm<br>48-QFN | 7 x 7 mm<br>48-QFN |

To request samples, download documentation or learn more visit: idt.com/clockmatrix

IDT, the IDT Logo, ClockMatrix and UFT are registered trademarks or trademarks of Integrated Device Technology, Inc., in the United States and other countries. All other trademarks are the property of their respective owners. © 2019. Integrated Device Technology, Inc. All Rights Reserved.